An ISA to S-100 Bus Converter Board

The main use of a converter board like this is to help migrate

PC-ISA board

chipsets to S-100 boards. By having access to the original ISA board

hardware one can checkout software and hardware issues more effectively.

One long term goal for example is to have a high resolution XVGA video board on

an S-100 bus board utilizing one of the many excellent PC video board chip sets

available. If we replicate the hardware correctly the "black box" software

on these ISA board ROMS should work without modifications. Here is a

picture of the final board:-

This board has its origins form an article I wrote back in 1985 for Micro/Systems Journal in which I described a S-100 board that allowed one to insert an IBM-PC 8 bit board into the S-100 bus

(see here). In particular it allowed one to utilize an S-100 8088 or 8086 CPU board with an IBM CGA and monochrome video board (which were not available for the S-100 bus at the time).

Below is a picture of that 1985 board.

The board was connected via a top ribbon cable to an IBM-PC bus board (made by I-Bus Systems).

While the board illustrated above worked reliably for IBM-PC type speeds, it was unsuitable for the higher S-100 bus speeds (~10 MHz) we have today with some of our boards. This is because the board utilized 74LS121 single shots to "synthesize" some of the critical

ISA signals. This is fine for a fixed low frequency system like the original PC. For clock frequency independence one should use shift registers to synthesize signals (see below).

Also it would be much more useful to utilize a PC-AT style 16 bit ISA bus so that more modern VGA type cards could be used. However going from 8 to 16 bits has a serious complication. In an PC-AT style system if a ISA card cannot accommodate a 16 bit data word it forces the CPU on the motherboard to sequentially send first the lower then upper 8 bit bytes, each with its own memory/IO read or write signals. The motherboard CPU only assumes a 16 bit data word will be accepted if it detects the ISA signals MEMCS16* or IOCS16* are low. If either are low the CPU immediately sends/receives the 16 bit data.

This is a bit of a complication for us, because most S-100 CPU boards (including our own S100Computers boards) do not have this capability. The S-100 IEEE-696 specifications does in fact describe it and an option but it was little used in the past because IEEE-696 S-100 bus RAM boards and the likes at the time could easily deal with 16 bit data. The lowered S-100 sXTRQ* line (Pin 58) was always acknowledged with a returned lower SIXTN* (pin 60). Older 8 bit only RAM boards simply had too small a capacity or speed to be useful.

That said, there were a few 8086 boards that did work with the older 8 bit RAM boards. The TecMar 8086 board is a good example. The manual clearly describes the sequential 16 bit to back to back 2X 8 bit transfer process. It was the starting point for the circuit below. However it does not provide two discrete read write signals -- something some of the ISA video chips seem to require (see below).

The ISA and S100 Bus Signals

Fortunately because both buses have as their basis Intel style origins, a number of the signals are very similar. For a thorough description of the bus signals I recommend the Sol Libes & Mark Garetz "Interfacing to S-100/IEEE696 Computers" and the Edward Solari "AT Bus Design" books.

The address lines are essentially similar for both buses. The upper ISA lines (A17-A23) are not latched (and in fact float during RAM refresh cycles), it is up to ISA boards to latch them. We will latch all address lines using the S-100 pSTVAL signal. This signal will also emulate the ISA BALE signal.

The ISA bus SBHE* comes directly from the Intel CPU indicating that the high byte on the bus is being processed. This is easily emulated on the S-100 bus:-

For mainly historic reasons the ISA bus has two Memory Read/Write signals depending on whether the CPU is talking to RAM on the motherboard or a card in the ISA bus. We will treat both as identical.

The ISA bus IOCHRDY has the same function as the S-100 bus XRDY & RDY signals, i.e. delay a CPU cycle for a slow memory or I/O access.

There are two clock signals on the ISA bus. The BCLK signal is essentially the CPU clock and will be provided by the S-100 bus Phi signal (pin 24). The second clock is mainly used by early PC video boards. It provides a 14.31818 MHz TV Color burst frequency.

The ISA bus has more interrupt pins than the 9 on the S-100 bus so we will use jumpers to select those needed. The ISA interrupts are normally edged triggered and any S-100 hardware (e.g. 8259A) would have to be programmed accordingly.

The ISA bus has 6 DMA request and acknowledge lines in contrast to the S-100 buss's 4. On the ISA bus all share a TC (terminal count) line use to indicate when a DMA transfer is complete. In it's current form, we will not implement ISA bus DMA control in the S-100 bus. It could be done, but if required it easier to do DMA on the S-100 side.

The remaining ISA signals are either straightforward or are

unutilized (pulled as required high or low).

There remains two critical aspects of this board we must address however. First we have to have a way where this board allows for "holes" in the S-100 bus memory space to allow access to on board RAM or ROMs on ISA boards. For example VGA boards commonly use RAM at B000:0H to B000H:FFFFH and a ROM at C000:0H to C000:7FFFH. We do this using 74LS682's to identify these windows in the S-100

bus's 16MG address space. If selected they activate the S-100 bus Phantom line (pin 67) thereby inactivating access on the S-100 side. Here is the circuit we use on the converter board:-

Likewise we need various I/O port address "holes" to access chips on the ISA bus boards. Fortunately these

board use 16 bit I/O port addressing and seldom the lower 256 I/O ports so there is seldom S-100 bus conflicts. Again we use 74LS682's to carve out I/O address spaces for ISA boards. For example most VGA ISA boards use ports in the 3B0H to 3DFH range. By using a two 74LS682's we can identify that range. Here is the circuit:-

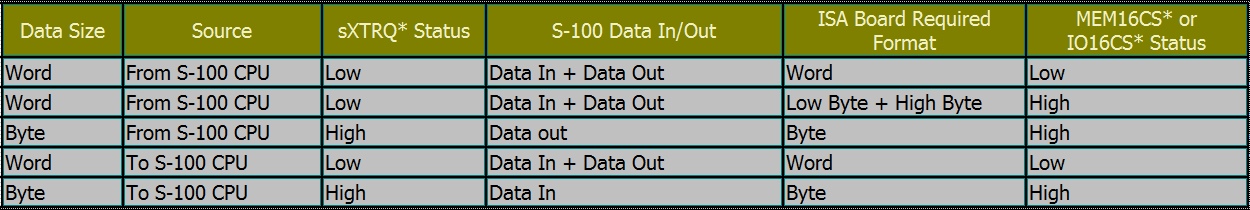

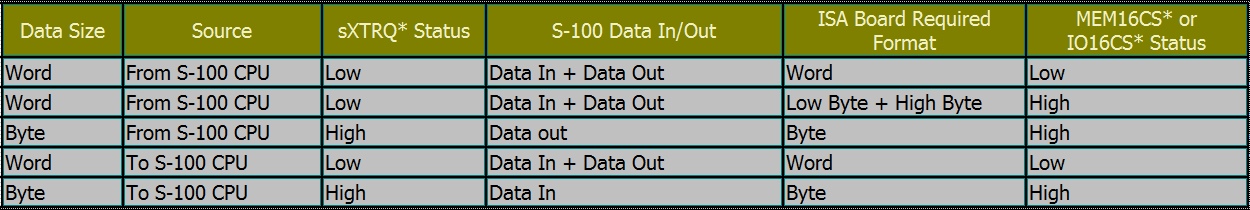

The second series of issues are far more challenging. Data transfers to and from the ISA bus can be in a number of formats:-

| |

|

Clearly we are going to have to tread very carefully as we

implement data transfers between the two bus's.

In order to have a converter board that is S-100 bus clock frequency independent we will use the S-100 Phi clock signal (Pin 24) to drive a shift register (a 74LS164) from which will be tapped sequentially various control signals. The problem case is when we wish to send a 16 bit word to an ISA board that can only accept byte data (RAM or I/O). This unfortunately is a common situation with VGA video controller chips. We need to hold the S-100 16 bit word (put the CPU in a wait state), send the low byte + write signal to the ISA board, wait, then send the high byte + write signal, then release the S-100 CPU from it's wait state and continue to the next bus cycle.

The circuit to do all this is illustrate here:-

Not only must we send

sequentially send low and high byte data but we must also send the appropriate read or write signals twice. Once for the low byte data,

then again for the high byte data. Some ISA hardware seems to allow one to load up the low and high bytes and send a single read or write signal but

unfortunately not the most critical, VGA controller chips. We send these dual signals with

the following circuit:-

Fortunately to debug this complicated situation we have one S-100 board that comes to

the rescue. Our S-100 8088 CPU board does within the CPU exactly what I described above. Internally its a 16 bit CPU but

externally it's 8 bit. It will always interact with an ISA board exactly as the IBM-PC does.

I used this board to first get our converter board working.

The Plan

Even with this we will step things along slowly. First we will work with an old IBM-PC CGA

video board not only because it is strictly 8 bit, but it does not require an

onboard ROM to initialize the board. We will then step up to an EGA video

board. This board does have an onboard ROM but the interface is well described

as is the software. It too is an 8 bit only ISA board. Next we will

utilize an 8 bit VGA video board, Then a true 16 bit ISA VGA board. All

these boards must work seamlessly with MSDOS V4.01 using the video board as a

standard IBM-PC console output.

Only then will we move to the more challenging 16 bit S-100 bus CPU using our (8086

CPU board) repeating the above steps. Here is a picture

of our first prototype board:-

You can see the ISA connector at the top of the board. There are no right

angled ISA connectors, so in order to get this arrangement I soldered the ISA

socket pins directly to a dual row set of right angled jumpers. (Jameco

#139564) cut to size.

First I tried the board with an old IBM-PC CGA video board. Frustratingly that

board (8 bit only data) does not fit into the ISA socket because the upper 32

pin section of the socket blocks the board seating properly. I had to place a

bus extender card in the lower 62 pin section of the ISA socket and then place

the CGA card in the extender board. Looked like a real kludge sticking way

up over the S-100 bus. But fortunately it worked.

Here is a picture of MSDOS V4.01 signing on using the above arrangement the

output going to an old PC video monitor.

To recap, what we have here is our S-100 8088 board directly driving a standard

IBM-PC video board utilizing our bus converter card.

Next I moved the ISA converter board up to working with an EGA board. I

used a "Basic Time" 1986 EGA clone board. It is driven by four C&T chips.

This is still an 8 bit bus board but unlike the above CGA board has its own

onboard EPROM (at C000:0H to C000:7FFFH).

Here is a picture of this arrangement:-

At first I ran into a problem with the display of characters on the screen. I

could fill video RAM with various colors starting at B000:0H (see below) but all

text characters appeared (in their correct positions) as white squares.

Only later did I find out that the EGA BIOS requires RAM access at A000:0 to

place a character lookup table. When I opened up the S-100 bus RAM "hole"

(see above) from A000:0 to B000:FFFFH the board worked perfectly. See the

display picture below:-

As I worked with this board I had to make numerous circuit changes and

alterations. It became clear that I would have to fabricate a second

prototype. I actually did another prototype board with numerous jumpers but

again found the circuits did not work correctly with 16 bit data transfers at

S100 bus speeds in the 8-10MHz range. In particular there was a problem

with ISA VGA boards during screen scrolls. When the ISA IO_READY signal was

being asserted. Long story short, if IO_READY went high while XRDY was

asserted by the shift register (U20) the sequential back to back 8 bit R/W's got

screwed up. The "stretching" of the critical signals got out of sync

with the video board.

Frustratingly I dropped this project for a number of months to rethink the whole

approach.

GAL's and PALAM

It became clear that to move forward with

this ISA to S100 bus converter board I was either going to have to design a very

detailed signal software emulation program or design a prototype board with

numerous jumpers with spare gates etc. to find a solution by trial and error.

The good news on the latter was I could easily run tight CPU loops

reading/writing words or bytes to a designated RAM or I/O port and analyze the

signals with an 8 input logic analyzed.

At about that time I discovered GAL's. These are chips that can be

programmed to emulate multiple AND, NAND, Inverter and FF gates -- all residing

in a single chip. I realize these chips may not be familiar to some users

so I have written up an introduction to them here (Introduction

to GAL's).

Please study that page

before going further if you are unfamiliar with GALs.

Another version of this ISA to S100 Bus Converter board was fabricated utilizing

GALs.

A GAL based ISA to S100 Bus Converter

Board.

It became apparent that the best way to experimentally make a converter board

like this was to utilize GAL's to try out various circuit arrangements.

GAL's allow you to quickly do what in 74LSxx chip hardware would be numerous and

extensive board alterations. I decide to use the 74LSxx chips just to

interface with the S100 bus and ISA bus and set up an onboard clocking

mechanism. Here is a picture of the prototype board:

Initially I decided to concentrate on an 8 bit only

ISA series of transfers. These can be of two types

1 8 bits to/from the S100 CPU to the ISA bus.

2 16 bits to/from the S100 CPU to the ISA bus.

In the case of the latter the 16 bits travel as two sequential 8 bit packets.

The ISA bus has have synthesized the double MEM or I/O Read/Write signals for

both back to back transfers. While this is taken place the S100 bus

CPU is held in a wait state. The final complication is that the ISA board can

(and often does) call for its own wait states (IO_READY) on the CPU.

These can strike at any time during or outside the above process. Clearly

accurate bus timing is critical. All timing is relative to the S100 bus

pSync signal. Here is the relevant circuit:

The 74LS164 (U20) provides shift delays relative to the start of an S100 bus,

bus cycle. Two things to note, via U4C, these shifts are only generated

when ISA_SEL and DUAL_REQUEST are both high. As we shall see ISA_SEL

is only high if an ISA board port or RAM area is selected. DUAL_REQUEST is only

selected if an S100 bus 16 bit data transfer is taking place and the ISA board

requires it to be transferred as two 8 bit back to back transfers. Here is

a picture of the logic levels coming out of U20 and used to pulse the ISA bus

MEMR signal.

The R_LOW and R_HIGH signals are then fed to another GAL to pulse the ISA

to S100 bus buffers.

Note that U13 is a 74LS374. This chip allows the data from the S100 bus to

be latched into U13 on the rising edge of the W_LOW signal and held there

after the address line is incremented to the odd/high byte. Here is the GAL code

to signal the timing inputs for the above 4 buffers.

There are a total of six 22V10 GAL's on the board. Three others

essentially supply the timed signals to the above two GAL's. The remaining

GAL which I call ABC_GAL is dedicated to driving bidirectional 8 bit (only) data

to/from the S100/ISA bus. This GAL also has the capability later to

drive bidirectional 16 bit data. This is not currently used (see below).

Here is a picture of the relevant circuit.

The source code for all 6 GAL's is available at the bottom of this page.

Please note, this is an experimental S100 board. The GAL's will be changed from

time to time to accommodate more PC-ISA boards. The current GALs are

written with the sole purpose of developing an 8 bit S100 bus XVGA video board.

While I have debugged this ISA converter board with an old IBM-PC CGA board, the

VGA test board is

Sergey's ISA Super VGA board. This simple but very reliable board is

well documented. The ROM BIOS code works with an 8088/8086 (i.e. does not

require 80286 or later opcodes) and it has a fast 8 bit interface for both the

ROM BIOS and video chip (a Trident TVGA9000i-3). Here is a picture of my

test bed arrangement:-

Here is a memory map of what you should see if the VGA board ROM is available to

the CPU.

It is very important to see the Video BIOS signon bytes 55H,AAH starting at

C000:0H in ROM. You need to show that they appear as such with the 8086

monitor using the RAM byte display command ("D") and the RAM word display

command ("W"). Unless the 8086 monitor sees this 55AA signature it will

not call the VGA BIOS initialization routine for a MSDOS boot routine.

Instead it will load MSDOS with the default system Console I/O routines.

BTW, if bit 2 of the SMB

IOBYTE port is set to 0 you can also bypass the VGA BIOS ROM (useful for

debugging). I have enlarged my VGA BIOS menu driven MSDOS program for

debugging these VGA boards. The menu below is fairly self evident.

The source is available at the bottom of this page.

The program is called "CIRRUS.COM" simply because it was first written to

debug a Cirrus 5420 VGA chip. (Some day I will get back to placing that

(more powerful) VGA chip on an S100 board). BTW, the above display is an example of the above Trident ISA board in our S100/ISA

bus adaptor board.

This very short and simple summary actually represents many hours of testing and

debugging. Invaluable was the

Saleae 16

line Logic probe. I have recently updated our 8086 (and

80386)

monitors to contain fast loops to continuously read/write both bytes and words

from RAM/ROM at C0000H. This really helps you fine tune the GAL codes to

get the right timing relationships between the buses. Here would be a

typical test situation:-

The next step is to take the core elements of this ISA converter board and the

Trident driven VGA board and place them on an S100 board bypassing all the

ISA bus connectors etc.

One problem I have found with this board is that this GAL conversion circuit

will only work with out 8088 and 8086 CPU boards. I have tried to get it

to work with the V1 and V2 80286 boards without success. For some reason

on those boards the wait states required to generate two 8 bit back to back

signals are not stretching out the 82288 Rd/Wr signals. More careful

analysis is clearly required.

My current thinking for boards past the 8086 board is to wait for the 80486 CPU

board I am doing. Because the 80486 can on the fly

talk to 8, 16 or 32 bit buses for any bus cycle, a VGA board as

described above is actually easy to interface and is next in line for

development.

Please not all the essential ISA control signals are generated within the GAL

chips. Theism allows you tremendous flexibility to control the timing of

the ISA signals. The bad news is you have to write code and program

these GALs. I use Lattice 22V10 GALs in all cases. They are

easily programmed using for example a

Wellon

VP-290 "Prom Burner".

A description of the software (PALASM) needed to "burn" these GAL's can be found

here

CORE GAL.pdf

EXTRA GAL.pdf

DUAL_8 GAL.pdf

ISA GAL.pdf

VGA IO GAL.pdf

ABC-GAL.pdf

VGA-GALS.zip

Cirrus.zip

The Final Production Board.

Based on the above prototype board lessons, a "production board" was fabricated.

Here is a picture of the final production board:-

Step By Step Building

the ISA to S-100 Bus Converter

Board

Since

this board will probably only be used by experienced users I will skip a detail

build description. The board is relatively straightforward to build

As always examine the bare board carefully for scratches or damaged

traces, use a magnifying glass if need be. The quality of the boards we get is

excellent, but there is always a first time. A broken trace is almost impossible to detect by eye on a completed board.

Next solder in all the required IC sockets, resistors, resistor arrays, capacitors, jumpers, and the voltage regulators.

Do not add the LED's or LED bar yet. Be sure you put the resistor arrays in with

the correct orientation of pin 1. Check their values before soldering (they are

difficult to remove).

The TO-3 5V regulator (U54) heat sink must not touch the traces under it. Use either a mica TO-3 insulator or two small nut washers to separate it from the board itself.

The reason for this large TO-3 regulator is because some older PC boards use

quite a bit of power. The chips on this S100 board get their 5 volts from

a 3 Amp TO-220 (U3) regulator (Mouser #511-LM323T). You can probably get

away with the 1.5 Amp types (egg Jameco # 924633) but I like to overkill. The

Lattice 22V10 GALs can be obtained from Jameco #39159). All the other

chips are standard 74LSxx series. Note U13 must be a 74LS374.

For prototype boards I generally use "double swipe" IC sockets. For a

production board like this I prefer to use "Machine Tooled" IC sockets. However they are more expensive and you have to be particularly careful not to bend the IC pins. The clock oscillator should have

its own special socket (e.g. Jameco #133006). The dip switches are best

soldered directly into the board.

The ISA bus connector is hard to find. I obtained mine from eBay.

A right handed connector does not exist. You have to make your own by

bending one row of pins at right angles. Soldering them to the board and use a

multi-row right angled header (Jameco # 103271) to connect the second row of

pins. Solder these pins to the second row of pins on the connector.

Please examine the picture below:-

If you have our 8088 CPU board

you can test this board with

Sergey's ISA Super VGA board in 8 bit only mode. You do not need

U13, U14, U22. U23, U25 or the DUAL_GAL (U37). Of course for the

8086 board they must be

present.

When you have all the chips inserted, check port addressing by inputting &

outputting to a VGA port such as 102H, 4CE8H, 3BxH, 3CxH, 0r 3DxH. The

appropriate LED's should flash. If you have our

8086 ROM

monitor running, use the "A" command and do a memory map. The VGA prom

should appear at C0000H - C7FFFH. Copy it to RAM and verify the copy

went OK. Use the "P" command to boot MS-DOS. The monitor

should recognize the VGA ROM and initialize the VGA chips. It will then boot

MSDOS with the MSDOS signon appearing on the VGA screen.

A Production S-100 Board

Realizing that a number of people might want to utilize a

board like this together with a group of

people on the

Google

Groups S100Computers Forum, "group purchases" are made from time to time.

Contact and join the group if you would like to be involved in this project.

Please see here for more

information.

The links below will contain the most recent schematic of this board.

Note, it may change over time and some IC part or pin numbers may not correlate

exactly with the text in the article above.

MOST

CURRENT PROTOTYPE BOARD SCHEMATIC

(V6, FINAL, 12/1/2014)

MOST

CURRENT PROTOTYPE BOARD LAYOUT (V6, FINAL,

12/1/2014)

ISA To S100

Bus board BOM

(2/24/2017

Supplied by Rick Bromagem)

Most current

KiCAD files for this board (TestIO Board KiCAD.zip

12/1/2014)

Other pages describing my S-100

hardware and software.

Please click

here

to continue...

This page was last modified on

11/30/2017

.jpg)